Today’s Xinwen reported on March 2 that on Tuesday, Eastern Time, the U.S. Department of Commerce released “Vision for Success: Commercial Manufacturing Facilities“, “Funding Opportunities-Commercial Manufacturing Facility Situation Table: Chip Project Office Startup Funding Opportunity Notice”, A series of documents such as the “Notice of Financing Opportunities (NOFO) Chip Incentive Plan” indicate that the application process for the US$52.7 billion chip industry subsidy is about to start.

According to the “Chip and Science Act” passed by the United States last year, $52.7 billion in federal funds will be provided to revitalize the U.S. semiconductor industry, including $39 billion in incentives for semiconductor plant construction/expansion, and $13.2 billion in R&D and workforce development , and $500 million to strengthen global supply chains. In the series of documents released this time, its chip project office announced three subsidy opportunities. In addition to introducing the application details for the first subsidy in detail, it put forward six “obligatory” requirements for applicants, and called out the five major “compulsories” of American chips. Century Ambition”.

01 Three Subsidy Opportunities

The public documents of the U.S. Department of Commerce show that in addition to the “first subsidy related to semiconductor manufacturing” announced this time, the chip project office is expected to release two additional subsidy opportunities: one for semiconductor materials and manufacturing equipment facilities in the late spring of 2023 , another research and development facility for fall 2023.

Among them, the newly announced incentive application for semiconductor manufacturing facilities will begin to accept pre-applications and complete applications for front-end facilities from March 31; from May 1, it will begin to accept applications for the current generation, mature nodes, and back-end production facilities. Pre-applications are available, and full applications are being accepted starting June 26.

Specific subsidies will come in the form of direct funds (through grants, cooperative agreements or other transactions), federal loans or debt guarantees, the Commerce Department said. The proportion of the specific subsidy still needs to be evaluated on a case-by-case basis. However, the U.S. Department of Commerce also mentioned in the guidelines that the sum of various subsidies is not expected to exceed 35% of the overall project expenditure, and the direct cash subsidy for most projects will fall between 5% and 15% of the capital expenditure. In terms of process, the application is divided into 5 stages: brief introduction of the project, project pre-application (optional step), complete application (including detailed information of the project, the two parties will draw up a non-binding preliminary memorandum of terms agreement), due diligence Investigation, preparation and distribution of subsidies. In terms of subsidy objects, the first subsidy plan will be aimed at four types of semiconductor manufacturing facilities:

Frontier facilities: In terms of logic chips, it currently includes equipment to produce high-capacity semiconductors using EUV lithography tools; in terms of memory, it currently includes 3D NAND flash memory chips capable of producing 200 layers and above, (and/or) DRAM chips of 13nm and below.

Facilities for current-generation nodes: 28nm process technology, including logic, analog, RF, and mixed-signal chips; cutting-edge technology equipment for fabrication at current-generation nodes, and new and specialized technologies, such as devices based on compound semiconductor materials.

Mature node facilities: not based on FinFET, post-FinFET transistor structures, or any other 28nm transistor structures; discrete semiconductor devices such as diodes and transistors; optoelectronic and optical semiconductors; sensors.

Back-end production facilities for assembly, testing, packaging, etc.: specifically geared toward ensuring operations that are competitive within the United States (such as automation).

02

Six “duties” for applicants

In order to subsidize huge amounts of funds, chip manufacturing giants such as TSMC, Samsung, and Intel competed for a while ago. But the money has not been received yet, and now that the application details for the first subsidy are released, the threshold and “obligations” in it may not have been expected by them. ”Obligation One”: Sharing excess profits with the US government. According to the documents, applicants who accept funds exceeding US$150 million need to reach an agreement with the US government. If the profitability of the project exceeds expectations, the applicant needs to return a certain percentage of funds to the government after reaching the agreed threshold. ”Obligation Two”: Provide childcare services for employees. Applicants who receive funding in excess of $150 million must provide a plan to provide affordable, accessible, reliable and high-quality child care for employees of the planned facility. ”Obligation Three”: Prohibit the use of subsidies for stock dividends and stock repurchases. Ban applicants from dividends and stock repurchases subsidized by the CHIP Act. Therefore, the applicant needs to provide the government with a stock repurchase plan for the next five years, and the applicant’s efforts to “restrain and limit stock repurchase” are also a consideration in the review process. But it is worth mentioning that Texas Instruments has promised investors that all surplus cash flow will be used for dividends or stock repurchases, and Intel is also known for its generous dividends. Now, these companies may need to adjust how they reward shareholders. ”Obligation Four”: six project priority areas must be addressed. Project priority applications must also involve the following six project priority areas:

Committed to future investment in the U.S. semiconductor industry, including plans to establish research and development facilities in the United States; Support chip research and development projects; Create opportunities for minority, veteran-owned and women-owned businesses; demonstrate climate and environmental esponsibility; Invest in their communities by addressing barriers to economic inclusion; Commitment to use American-produced steel and building materials.

“Obligation Five”: Comply with the “Guardrail Clause” In addition, the chip project office once again emphasized the “guardrail” clause, requiring: Applicants must return full subsidy funds if they knowingly conduct joint research or technology licensing work “with a foreign entity that raises national security concerns”. In addition, successful applicants for the subsidy must agree not to engage in certain major transactions involving “expansion of semiconductor manufacturing capabilities in the country concerned” for a period of 10 years from the date of receiving the subsidy. ”Obligation Six”: Participate in and support the chip research and development of US institutions。 However, unlike the “strict foreign research cooperation requirements”, applicants have many “obligations” for research in the United States: Each applicant will be required to participate in the National Semiconductor Technology Center (NSTC) in the United States, which conducts research and prototyping of advanced semiconductor technologies; or to participate in, support, and collaborate on projects funded by the National Advanced Packaging Manufacturing Program (NAPMP). Applicants will further be required to submit commitments to support these or other chip R&D efforts, such as rotating project technicians to NSTC or NAPMP, or providing mature node process design kits under open source licenses, to further strengthen the U.S. electronic design automation industry and improve Manufacturing interoperability.

03

The “Century Vision” of American Chips

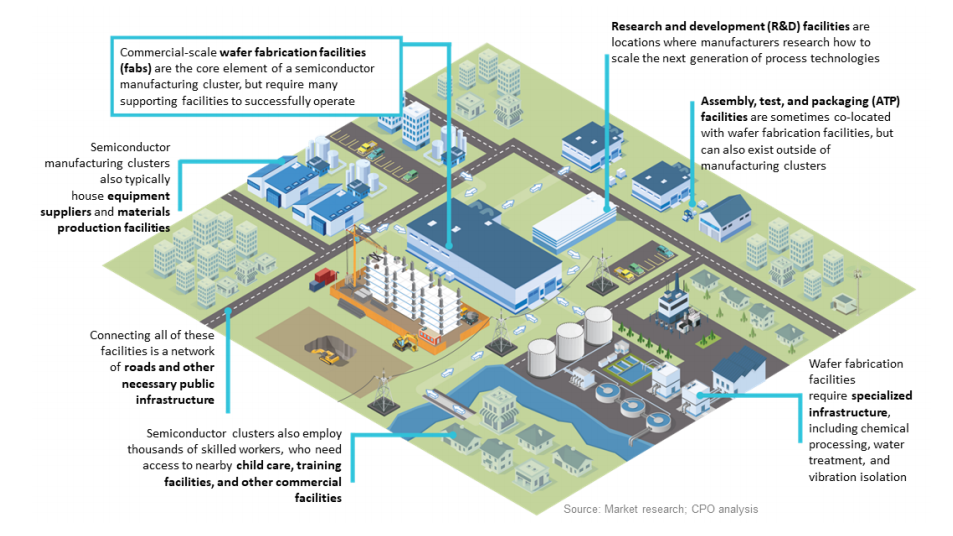

In addition to the aforementioned subsidy rules, in “Vision for Success: Commercial Manufacturing Facilities”, the chip project office targets cutting-edge logic chips, advanced packaging, advanced DRAM chips, current generation and mature node chips, compound semiconductors and other specialty chips. Taking “the end of this century” as the node, the corresponding planning and “ambition” are put forward: The U.S. is expected to have at least two new large-scale clusters of leading-edge logic fabs by the end of the decade, and is expected to focus its leading-edge logic investments on at least two clusters of companies manufacturing highly advanced chips in the United States.

Considering the importance of advanced packaging to leading-edge logic and memory, it is planned that by the end of this century, the United States will have multiple high-volume advanced packaging facilities. Homegrown U.S. fabs can produce high-capacity leading-edge DRAM chips “on economically competitive terms,” and plans to conduct R&D in the U.S. on next-generation memory technologies critical to supercomputing and other applications.

By the end of the century, the United States will increase production of current-generation and mature-node chips that are critical to the economy and security; and will coordinate with allies and partners to ensure resilient production and use of current-generation and mature-node chips . The United States will increase production of compound semiconductors and other specialty chips and maintain its technological leadership.

From: Kelvin’s/Core news today

Post time: Mar-06-2023